6.1 Uvod

Postoje dvije vrste modernih računala opće namjene: CISC i RISC. CISC je kratica za Complex Instruction Set Computer. RISK je kratica za Reduced Instruction Set Computer. Mikroprocesori 6502 ili 6510, primjenjivi na računalo Commodore-64, više nalikuju RISC arhitekturi nego CISC arhitekturi.

RISC računala općenito imaju kraće asemblerske instrukcije (po broju bajtova) u usporedbi s CISC računalima.

Bilješka : Bilo da se radi o CISC-u, RISC-u ili starom računalu, periferni uređaj počinje od unutarnjeg priključka i ide prema van kroz vanjski priključak na okomitoj površini sistemske jedinice računala (bazne jedinice) do vanjskog uređaja.

Tipična instrukcija CISC računala može se promatrati kao spajanje nekoliko kratkih instrukcija na asemblerskom jeziku u jednu dužu instrukciju na asemblerskom jeziku, što jednu rezultirajuću instrukciju čini složenom. Konkretno, CISC računalo učitava operande iz memorije u registre mikroprocesora, izvodi operaciju, a zatim pohranjuje rezultat natrag u memoriju, sve u jednoj instrukciji. S druge strane, ovo su barem tri upute (kratke) za RISC računalo.

Postoje dvije popularne serije CISC računala: Intel mikroprocesorska računala i AMD mikroprocesorska računala. AMD je kratica za Advanced Micro Devices; to je tvrtka za proizvodnju poluvodiča. Intelove serije mikroprocesora, prema redoslijedu razvoja, su 8086, 8088, 80186, 80286, 80386, 80486, Pentium, Core, i Series, Celeron i Xeon. Upute asemblerskog jezika za rane Intelove mikroprocesore kao što su 8086 i 8088 nisu jako složene. Međutim, oni su složeni za nove mikroprocesore. Najnoviji AMD mikroprocesori za seriju CISC su Ryzen, Opteron, Athlon, Turion, Phenom i Sempron. Intel i AMD mikroprocesori poznati su kao x86 mikroprocesori.

ARM je kratica za Advanced RISC Machine. ARM arhitekture definiraju obitelj RISC procesora koji su prikladni za korištenje u širokom spektru aplikacija. Dok se mnogi Intel i AMD mikroprocesori koriste u stolnim osobnim računalima, mnogi ARM procesori služe kao ugrađeni procesori u sigurnosnim kritičnim sustavima kao što su automobilski sustavi protiv blokiranja kotača i kao procesori opće namjene u pametnim satovima, prijenosnim telefonima, tabletima i prijenosnim računalima . Iako se obje vrste mikroprocesora mogu vidjeti u malim i velikim uređajima, RISC mikroprocesori se više nalaze u malim nego u velikim uređajima.

Računalna riječ

Ako se za računalo kaže da je računalo od 32 bita, to znači da se informacije pohranjuju, prenose i njima manipulira u obliku tridesetdvobitnih binarnih kodova unutar unutarnjeg dijela matične ploče. To također znači da su registri opće namjene u mikroprocesoru računala široki 32 bita. Registri A, X i Y mikroprocesora 6502 su registri opće namjene. Široki su osam bita, pa je tako računalo Commodore-64 osmobitno računalo riječi.

Neki rječnik

X86 Računala

Značenja bajta, riječi, dvostruke riječi, četveroriječi i dvostruke četveroriječi su sljedeća za x86 računala:

- Bajt : 8 bita

- Riječ : 16 bita

- Dvostruka riječ : 32 bita

- Četveroriječ : 64 bita

- Dvostruka četveroriječ : 128 bita

ARM računala

Značenja bajta, poluriječi, riječi i dvostruke riječi su sljedeća za ARM računala:

- Bajt : 8 bita

- Postani pola : 16 bita

- Riječ : 32 bita

- Dvostruka riječ : 64 bita

Treba primijetiti razlike i sličnosti za x86 i ARM imena (i vrijednosti).

Bilješka : Cijeli brojevi predznaka u obje vrste računala komplement su dva.

Mjesto memorije

S Commodore-64 računalom, memorijska lokacija obično je jedan bajt, ali povremeno može biti dva uzastopna bajta kada se uzmu u obzir pokazivači (neizravno adresiranje). S modernim x86 računalom, memorijska lokacija je 16 uzastopnih bajtova kada se radi s dvostrukom četveroriječju od 16 bajtova (128 bita), 8 uzastopnih bajtova kada se radi s četveroriječju od 8 bajtova (64 bita), 4 uzastopna bajta kada se radi s dvostrukom riječi od 4 bajta (32 bita), 2 uzastopna bajta kada se radi o riječi od 2 bajta (16 bita) i 1 bajt kada se radi o bajtu (8 bita). S modernim ARM računalom, memorijska lokacija je 8 uzastopnih bajtova kada se radi s dvostrukom riječi od 8 bajtova (64 bita), 4 uzastopna bajta kada se radi s riječju od 4 bajta (32 bita), 2 uzastopna bajta kada se radi s poluriječju od 2 bajta (16 bita) i 1 bajta kada se radi o bajtu (8 bita).

Ovo poglavlje objašnjava što je zajedničko u CISC i RISC arhitekturama i koje su njihove razlike. To je učinjeno u usporedbi s 6502 µP i commodore-64 računalom gdje je primjenjivo.

6.2 Blok dijagram matične ploče modernog računala

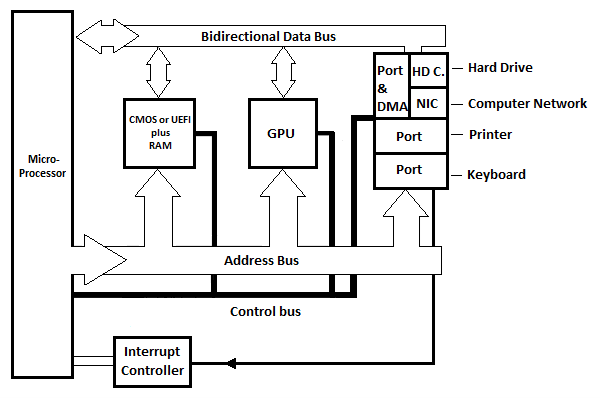

PC je kratica za osobno računalo. Slijedi generički osnovni blok dijagram za modernu matičnu ploču s jednim mikroprocesorom za osobno računalo. Predstavlja CISC ili RISC matičnu ploču.

Slika 6.21 Osnovni blok dijagram matične ploče modernog osobnog računala

Na dijagramu su prikazana tri unutarnja priključka, ali u praksi ih ima više. Svaki port ima registar koji se može vidjeti kao sam port. Svaki krug porta ima najmanje još jedan registar koji se može nazvati 'statusni registar'. Registar statusa označava priključak za program koji šalje signal prekida mikroprocesoru. Postoji sklop kontrolera prekida (nije prikazan) koji razlikuje različite linije prekida iz različitih priključaka i ima samo nekoliko linija do µP.

HD.C u dijagramu označava karticu tvrdog diska. NIC je kratica za karticu mrežnog sučelja. Kartica tvrdog diska (sklop) povezana je s tvrdim diskom koji se nalazi unutar osnovne jedinice (jedinice sustava) modernog računala. Kartica mrežnog sučelja (krug) je preko vanjskog kabela spojena na drugo računalo. Na dijagramu postoji jedan priključak i DMA (pogledajte sljedeću ilustraciju) koji su spojeni na karticu tvrdog diska i/ili na karticu mrežnog sučelja. DMA je kratica za izravni pristup memoriji.

Upamtite iz poglavlja o računalu Commodore-64 da za slanje bajtova iz memorije u pogon diska ili drugo računalo, svaki bajt mora biti kopiran u registar u mikroprocesoru prije nego što se kopira na odgovarajući interni port, a zatim automatski na uređaj. Kako bi primili bajtove s pogona diska ili drugog računala u memoriju, svaki bajt mora biti kopiran iz odgovarajućeg internog registra porta u registar mikroprocesora prije nego što se kopira u memoriju. Ovo obično traje dugo ako je broj bajtova u toku velik. Rješenje za brz prijenos je korištenje izravnog pristupa memoriji (sklop) bez prolaska kroz mikroprocesor.

DMA sklop je između porta i HD-a. C ili NIC. S izravnim pristupom memoriji DMA sklopa, prijenos velikih tokova bajtova je izravno između DMA sklopa i memorije (RAM) bez daljnjeg sudjelovanja mikroprocesora. DMA koristi adresnu sabirnicu i podatkovnu sabirnicu umjesto µP. Ukupno trajanje prijenosa je kraće nego ako se koristi µP hard. I HD C. ili NIC koriste DMA kada imaju veliki tok podataka (bajtova) za prijenos s RAM-om (memorija).

GPU je kratica za Graphics Processing Unit. Ovaj blok na matičnoj ploči odgovoran je za slanje teksta i pokretnih ili nepokretnih slika na zaslon.

Kod modernih računala (PC) nema memorije samo za čitanje (ROM). Postoji, međutim, BIOS ili UEFI koji je vrsta trajnog RAM-a. Informacije u BIOS-u zapravo održava baterija. Baterija je ono što zapravo održava i tajmer sata, u pravo vrijeme i datum za računalo. UEFI je izumljen nakon BIOS-a i zamijenio je BIOS iako je BIOS još uvijek prilično bitan u modernim računalima. O tome ćemo više razgovarati kasnije!

U modernim osobnim računalima, adresne i podatkovne sabirnice između µP i internih portova (i memorije) nisu paralelne sabirnice. To su serijske sabirnice koje trebaju dva vodiča za prijenos u jednom smjeru i još dva vodiča za prijenos u suprotnom smjeru. To znači, na primjer, da se 32-bita mogu slati u seriji (jedan bit za drugim) u bilo kojem smjeru.

Ako je serijski prijenos samo u jednom smjeru s dva vodiča (dvije linije), kaže se da je to half-duplex. Ako je serijski prijenos u oba smjera s četiri vodiča, po jedan par u oba smjera, kaže se da je full-duplex.

Cijela memorija modernog računala još uvijek se sastoji od niza lokacija bajtova: osam bita po bajtu. Moderno računalo ima memorijski prostor od najmanje 4 gigabajta = 4 x 210 x 2 10 x 2 10 = 4 x 1,073,741,824 10 bajtova = 4 x 1024 10/pod> x 1024 10 x 1024 10 = 4 x 1,073,741,824 10 .

Bilješka : Iako na prethodnoj matičnoj ploči nije prikazan tajmerski krug, sve moderne matične ploče imaju tajmerske krugove.

6.3 Osnove arhitekture računala x64

6.31 Skup registara x64

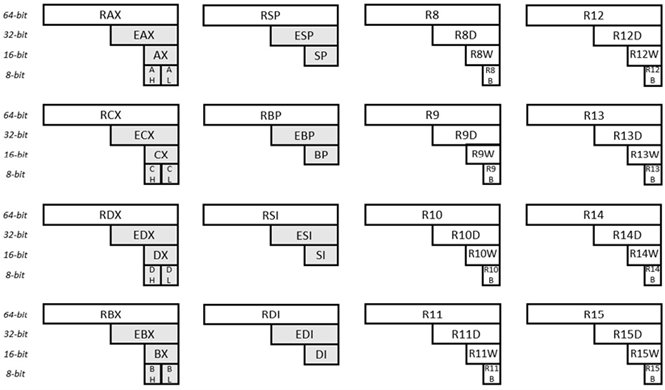

64-bitni mikroprocesor x86 serije mikroprocesora je 64-bitni mikroprocesor. Prilično je moderno zamijeniti 32-bitni procesor iste serije. Registri opće namjene 64-bitnog mikroprocesora i njihovi nazivi su sljedeći:

Slika 6.31 Registri opće namjene za x64

Šesnaest (16) registara opće namjene prikazano je na danoj slici. Svaki od ovih registara je širok 64 bita. Gledajući registar u gornjem lijevom kutu, 64 bita su identificirana kao RAX. Prva 32 bita ovog istog registra (s desna) identificirana su kao EAX. Prvih 16 bitova ovog istog registra (s desna) identificirani su kao AX. Drugi bajt (s desna) ovog istog registra identificiran je kao AH (H ovdje znači visoko). A prvi bajt (istog ovog registra) identificiran je kao AL (L ovdje znači nisko). Gledajući registar u donjem desnom kutu, 64 bita su identificirana kao R15. Prva 32 bita ovog istog registra identificirana su kao R15D. Prvih 16 bitova istog registra identificirano je kao R15W. I prvi bajt je identificiran kao R15B. Slično su objašnjeni i nazivi ostalih upisnika (i podupisnika).

Postoje neke razlike između Intel i AMD µP. Informacije u ovom odjeljku odnose se na Intel.

Kod 6502 µP, registar programskog brojača (nije dostupan izravno) koji sadrži sljedeću instrukciju koju treba izvršiti širok je 16 bita. Ovdje (x64), programski brojač se naziva Instruction Pointer, i širok je 64 bita. Označen je kao RIP. To znači da x64 µP može adresirati do 264 = 1,844674407 x 1019 (zapravo 18,446,744,073,709,551,616) memorijskih bajt lokacija. RIP nije registar opće namjene.

Stack Pointer Register ili RSP jedan je od 16 registara opće namjene. Pokazuje na zadnji unos hrpe u memoriji. Kao i kod 6502 µP, stog za x64 raste prema dolje. S x64, stog u RAM-u koristi se za pohranjivanje povratnih adresa za potprograme. Također se koristi za pohranu 'prostora sjene' (pogledajte sljedeću raspravu).

6502 µP ima 8-bitni statusni registar procesora. Ekvivalent u x64 se zove RFLAGS registar. Ovaj registar pohranjuje oznake koje se koriste za rezultate operacija i za upravljanje procesorom (µP). Širok je 64 bita. Viša 32 bita su rezervirana i trenutno se ne koriste. Sljedeća tablica daje nazive, indekse i značenja često korištenih bitova u registru RFLAGS:

| Tablica 6.31.1 Najčešće korištene RFLAGS zastavice (bitovi) |

|||

|---|---|---|---|

| Simbol | bit | Ime | Svrha |

| CF | 0 | nositi | Postavlja se ako aritmetička operacija generira prijenos ili posuđivanje iz najznačajnijeg bita rezultata; drugačije očišćeno. Ova zastavica označava uvjet preljeva za aritmetiku cijelog broja bez predznaka. Također se koristi u aritmetici višestruke preciznosti. |

| PF | 2 | Paritet | Postavlja se ako najmanje značajan bajt rezultata sadrži paran broj od 1 bitova; drugačije očišćeno. |

| OD | 4 | prilagoditi | Postavlja se ako aritmetička operacija generira prijenos ili posuđivanje iz bita 3 rezultata; drugačije očišćeno. Ova se zastavica koristi u binarno kodiranoj decimalnoj (BCD) aritmetici. |

| ZF | 6 | Nula | Postavlja se ako je rezultat nula; drugačije očišćeno. |

| SF | 7 | Znak | Postavlja se ako je jednak bitu najveće važnosti rezultata koji je bit predznaka cijelog broja s predznakom (0 označava pozitivnu vrijednost, a 1 negativnu vrijednost). |

| OD | jedanaest | Prelijevanje | Postavlja se ako je cjelobrojni rezultat preveliki pozitivni broj ili premali negativni broj (isključujući predznak-bit) da stane u odredišni operand; drugačije očišćeno. Ova zastavica označava uvjet preljeva za aritmetiku cijelog broja s predznakom (komplement dva). |

| DF | 10 | Smjer | Postavlja se ako instrukcije niza smjerova rade (povećanje ili smanjenje). |

| iskaznica | dvadeset i jedan | Identifikacija | Postavlja se ako njegova promjenjivost označava prisutnost CPUID instrukcije. |

Uz osamnaest 64-bitnih registara koji su prethodno navedeni, x64 arhitektura µP ima osam 80-bitnih širokih registara za aritmetiku s pomičnim zarezom. Ovih osam registara također se mogu koristiti kao MMX registri (pogledajte sljedeću raspravu). Također postoji šesnaest 128-bitnih registara za XMM (pogledajte sljedeću raspravu).

To nije sve o registrima. Postoji više x64 registara koji su segmentni registri (uglavnom se ne koriste u x64), kontrolni registri, registri za upravljanje memorijom, registri za otklanjanje pogrešaka, virtualizacijski registri, registri performansi koji prate sve vrste unutarnjih parametara (pogoci/promašaji predmemorije, izvršene mikro operacije, vrijeme , i mnogo više).

SIMD

SIMD je kratica za Single Instruction Multiple Data. To znači da jedna instrukcija asemblerskog jezika može djelovati na više podataka u isto vrijeme u jednom mikroprocesoru. Razmotrite sljedeću tablicu:

| 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | |

| + | 9 | 10 | jedanaest | 12 | 13 | 14 | petnaest | 16 |

| = | 10 | 12 | 14 | 16 | 18 | dvadeset | 22 | 24 |

U ovoj tablici, osam parova brojeva se dodaje paralelno (u istom trajanju) da bi se dobilo osam odgovora. Jedna instrukcija asemblerskog jezika može napraviti osam paralelnih zbrajanja cijelih brojeva u MMX registrima. Slično se može učiniti s XMM registrima. Dakle, postoje MMX upute za cijele brojeve i XMM upute za float.

6.32 Mapa memorije i x64

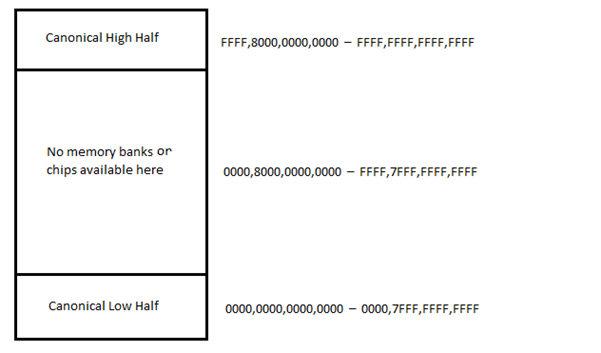

Uz pokazivač instrukcija (programski brojač) koji ima 64 bita, to znači da se može adresirati 264 = 1,844674407 x 1019 memorijskih bajtova. U heksadecimalnom sustavu, lokacija najvišeg bajta je FFFF,FFFF,FFFF,FFFF16. Niti jedno obično računalo danas ne može pružiti tako velik memorijski (kompletan) prostor. Dakle, prikladna mapa memorije za x64 računalo je sljedeća:

Primijetite da razmak od 0000,8000,0000,000016 do FFFF,7FFF,FFFF,FFFF16 nema memorijskih lokacija (nema memorijskih RAM banaka). Ovo je razlika od FFFF,0000,0000,000116 koja je prilično velika. Kanonska visoka polovica ima operativni sustav, dok kanonska niska polovica sadrži korisničke programe (aplikacije) i podatke. Operativni sustav sastoji se od dva dijela: malog UEFI (BIOS) i velikog dijela koji se učitavaju s tvrdog diska. Sljedeće poglavlje govori više o modernim operativnim sustavima. Obratite pažnju na sličnost s ovom memorijskom mapom i onom za Commodore-64 kada je 64KB moglo izgledati kao puno memorije.

U ovom kontekstu, operativni sustav se grubo naziva 'kernel'. Kernel je sličan Kernalu Commodore-64 računala, ali ima mnogo više potprograma.

Endianness za x64 je little endian, što znači da za lokaciju niža adresa pokazuje na niži bajt sadržaja u memoriji.

6.33 Načini adresiranja asemblerskog jezika za x64

Načini adresiranja su načini na koje instrukcija može pristupiti µP registrima i memoriji (uključujući interne port registre). x64 ima mnogo načina adresiranja, ali ovdje se govori samo o najčešće korištenim načinima adresiranja. Opća sintaksa za instrukcije ovdje je:

opcode odredište, izvor

Decimalni brojevi pišu se bez prefiksa ili sufiksa. Kod 6502, izvor je implicitan. X64 ima više operativnih kodova od 6502, ali neki od operativnih kodova imaju istu mnemoniku. Pojedinačne x64 upute su promjenjive duljine i mogu biti u rasponu veličine od 1 do 15 bajtova. Najčešće korišteni načini adresiranja su sljedeći:

Način trenutnog adresiranja

Ovdje je izvorni operand stvarna vrijednost, a ne adresa ili oznaka. Primjer (pročitajte komentar):

DODAJ EAX, 14 ; dodajte decimalni 14 u 32-bitni EAX od 64-bitnog RAX-a, odgovor ostaje u EAX-u (odredište)

Registrirajte se za način registracije adresiranja

Primjer:

DODAJ R8B, AL ; dodajte 8-bitni AL RAX-a u R8B 64-bitnog R8 – odgovori ostaju u R8B (odredište)

Način neizravnog i indeksiranog adresiranja

Neizravno adresiranje s 6502 µP znači da lokacija dane adrese u instrukciji ima efektivnu adresu (pokazivač) konačne lokacije. Slično se događa s x64. Indeksno adresiranje s 6502 µP znači da se sadržaj µP registra dodaje danoj adresi u instrukciji kako bi se dobila efektivna adresa. Slično se događa s x64. Također, s x64, sadržaj registra također se može pomnožiti s 1 ili 2 ili 4 ili 8 prije nego što se doda danoj adresi. Instrukcija mov (copy) x64 može kombinirati neizravno i indeksirano adresiranje. Primjer:

MOV R8W, 1234[8*RAX+RCX] ; pomakni riječ na adresi (8 x RAX + RCX) + 1234

Ovdje R8W ima prvih 16 bitova R8. Dana adresa je 1234. RAX registar ima 64-bitni broj koji se množi s 8. Rezultat se dodaje sadržaju 64-bitnog RCX registra. Ovaj drugi rezultat dodaje se danoj adresi koja je 1234 da bi se dobila efektivna adresa. Broj na mjestu efektivne adrese premješta se (kopira) na prvo 16-bitno mjesto (R8W) registra R8, zamjenjujući sve što je tamo bilo. Obratite pozornost na korištenje uglatih zagrada. Zapamtite da je riječ u x64 široka 16 bita.

RIP relativno adresiranje

Za 6502 µP, relativno adresiranje se koristi samo s uputama za grananje. Tamo je jedini operand operacijskog koda pomak koji se dodaje ili oduzima sadržaju programskog brojača za efektivnu adresu instrukcije (ne adresu podataka). Slično se događa s x64 gdje se programski brojač poziva kao pokazivač instrukcija. Instrukcija s x64 ne mora biti samo instrukcija grananja. Primjer RIP-relativnog adresiranja je:

MOV AL, [RIP]

AL of RAX ima 8-bitni broj s predznakom koji se dodaje ili oduzima od sadržaja u RIP-u (64-bitni pokazivač instrukcija) kako bi pokazao na sljedeću instrukciju. Imajte na umu da su izvor i odredište iznimno zamijenjeni u ovoj uputi. Također obratite pozornost na korištenje uglatih zagrada koje se odnose na sadržaj RIP-a.

6.34 Često korištene upute za x64

U sljedećoj tablici * označava različite moguće sufikse podskupa operativnih kodova:

| Tablica 6.34.1 Često korištene upute u x64 |

|

|---|---|

| Opcijski kod | Značenje |

| MOV | Premještanje (kopiranje) u/iz/između memorije i registara |

| CMOV* | Razni uvjetni potezi |

| XCHG | Razmjena |

| BSWAP | Zamjena bajtova |

| PUSH/POP | Upotreba hrpe |

| ADD/ADC | Dodati/sa nošenjem |

| SUB/SBC | Oduzimanje/s prenošenjem |

| MUL/IMUL | Množenje/bez predznaka |

| DIV/IDIV | Dijeli/bez predznaka |

| INC/DEC | Povećaj/Smanji |

| NEG | Negirati |

| CMP | Usporedi |

| I/ILI/XILI/NE | Bitove operacije |

| SHR/SAR | Logički/aritmetički pomak desno |

| SHL/SAL | Pomak ulijevo logički/aritmetički |

| ROR/ULOGA | Rotirajte desno/lijevo |

| RCR/RCL | Rotirajte desno/lijevo kroz nastavak za nošenje |

| BT/BTS/BTR | Bit test/i postavljanje/i resetiranje |

| JMP | Bezuvjetni skok |

| JE/JNE/JC/JNC/J* | Skoči ako je jednako/nije jednako/ nosi/ne nosi/mnogo drugih |

| ŠETAJ/ŠETAJ/ŠETAJ | Petlja s ECX-om |

| POZIV/POVLAČENJE | Poziv potprograma/povratak |

| NOP | Bez operacije |

| CPUID | CPU informacije |

x64 ima upute za množenje i dijeljenje. Ima hardverske sklopove za množenje i dijeljenje u svom µP. 6502 µP nema hardverske sklopove za množenje i dijeljenje. Množenje i dijeljenje je brže obaviti hardverski nego softverski (uključujući pomicanje bitova).

Upute za nizove

Postoji niz instrukcija niza, ali jedina o kojoj treba raspravljati ovdje je MOVS (za premještanje niza) instrukcija za kopiranje niza koji počinje na adresi C000 H . Za početak na adresi C100 H , koristite sljedeće upute:

MOVS [C100H], [C000H]

Obratite pažnju na sufiks H za heksadecimalno.

6.35 Petlja u x64

6502 µP ima upute za grananje za petlju. Instrukcija grananja skače na mjesto adrese koja ima novu instrukciju. Mjesto adrese može se nazvati 'petlja'. x64 ima LOOP/LOOPE/LOOPNE upute za petlju. Ove rezervirane riječi asemblerskog jezika ne smiju se brkati s oznakom 'petlja' (bez navodnika). Ponašanje je sljedeće:

LOOP smanjuje ECX i provjerava nije li ECX nula. Ako je taj uvjet (nula) ispunjen, skače se na određenu oznaku. U suprotnom, pada (nastavite s ostatkom uputa u sljedećoj raspravi).

LOOPE smanjuje ECX i provjerava da ECX nije nula (na primjer može biti 1) i da je ZF postavljen (na 1). Ako su ovi uvjeti ispunjeni, skače na etiketu. U suprotnom, propada.

LOOPNE smanjuje ECX i provjerava da ECX nije nula i da ZF NIJE postavljen (tj. da je nula). Ako su ti uvjeti zadovoljeni, prelazi na oznaku. U suprotnom, propada.

Kod x64, RCX registar ili njegovi poddijelovi kao što su ECX ili CX, drže cijeli broj brojača. Uz upute LOOP, brojač normalno odbrojava, smanjujući se za 1 za svaki skok (petlju). U sljedećem segmentu koda u petlji, broj u registru EAX povećava se od 0 do 10 u deset ponavljanja, dok se broj u ECX broji (smanjuje) 10 puta (pročitajte komentare):

MOV EAX, 0;

MOV ECX, 10; odbrojavanje prema zadanim postavkama 10 puta, jednom za svaku iteraciju

označiti:

INC EAX ; povećati EAX kao tijelo petlje

Oznaka PETLJE ; smanjite EAX, a ako EAX nije nula, ponovno izvršite tijelo petlje iz “oznake:”

Kodiranje petlje počinje s 'oznaka:'. Obratite pozornost na korištenje dvotočke. Kodiranje petlje završava oznakom 'LOOP' koja kaže smanjenje EAX. Ako njegov sadržaj nije nula, vratite se na instrukciju nakon 'oznake:' i ponovno izvedite bilo koju instrukciju (sve upute tijela) koja dolazi prema dolje do 'oznake PETLJE'. Imajte na umu da 'oznaka' još uvijek može imati drugo ime.

6.36 Ulaz/izlaz x64

Ovaj dio poglavlja bavi se slanjem podataka na izlazni (interni) port ili primanjem podataka s ulaznog (internog) porta. Čipset ima osmobitne portove. Bilo koja dva uzastopna 8-bitna porta mogu se tretirati kao 16-bitni port, a bilo koja četiri uzastopna porta mogu biti 32-bitni port. Na taj način procesor može prenijeti 8, 16 ili 32 bita na ili s vanjskog uređaja.

Informacije se mogu prenijeti između procesora i unutarnjeg priključka na dva načina: korištenjem onoga što je poznato kao memorijski mapirani ulaz/izlaz ili korištenjem zasebnog ulazno/izlaznog adresnog prostora. Memorijski mapirani I/O je sličan onome što se događa s procesorom 6502 gdje su adrese portova zapravo dio cijelog memorijskog prostora. U ovom slučaju, kada se podaci šalju na određenu adresnu lokaciju, oni idu u priključak, a ne u memorijsku banku. Portovi mogu imati zaseban I/O adresni prostor. U ovom drugom slučaju, sve memorijske banke imaju svoje adrese od nule. Postoji zaseban raspon adresa od 0000H do FFFF16. Koriste ih priključci u čipsetu. Matična ploča je programirana kako ne bi došlo do brkanja između memorijsko mapiranog I/O i odvojenog I/O adresnog prostora.

Memorijski mapirani I/O

Ovime se priključci smatraju memorijskim lokacijama, a normalni operacijski kodovi koji se koriste između memorije i µP koriste se za prijenos podataka između µP i priključnica. Dakle, da premjestite bajt iz priključka na adresi F000H u µP registar RAX:EAX:AX:AL, učinite sljedeće:

MOV AL, [F000H]

Niz se može premjestiti iz memorije u port i obrnuto. Primjer:

MOVS [F000H], [C000H]; izvor je C000H, a odredište je luka na F000H.

Odvojeni I/O adresni prostor

Pri tome se moraju koristiti posebne upute za ulaz i izlaz.

Prijenos pojedinačnih stavki

Registar procesora za prijenos je RAX. Zapravo, to je RAX:EAX za duplu riječ, RAX:EAX:AX za riječ i RAX:EAX:AX:AL za bajt. Dakle, za prijenos bajta s porta na FFF0h, u RAX:EAX:AX:AL, upišite sljedeće:

U AL, [FFF0H]

Za povratni prijenos upišite sljedeće:

IZLAZ [FFF0H], AL

Dakle, za pojedinačne stavke, upute su IN i OUT. Adresa porta također se može dati u RDX:EDX:DX registru.

Prijenos nizova

Niz se može prenijeti iz memorije u port čipseta i obrnuto. Za prijenos niza s priključka na adresi FFF0H u memoriju, počevši od C100H, upišite:

INS [ESI], [DX]

koji ima isti učinak kao:

INS [EDI], [DX]

Programer bi trebao staviti dvobajtnu adresu porta FFF0H u registar RDX:EDX:Dx i trebao bi staviti dvobajtnu adresu C100H u RSI:ESI ili RDI:EDI registar. Za obrnuti prijenos učinite sljedeće:

INS [DX], [ESI]

koji ima isti učinak kao:

INS [DX], [EDI]

6.37 The Stack u x64

Kao i procesor 6502, procesor x64 također ima hrpu u RAM-u. Stog za x64 može biti 2 16 = 65,536 bajtova ili može biti 2 32 = 4.294.967.296 bajtova. Također raste prema dolje. Kada se sadržaj registra gurne na stog, broj u pokazivaču RSP stoga smanjuje se za 8. Zapamtite da je memorijska adresa za x64 široka 64 bita. Vrijednost u pokazivaču stoga u µP pokazuje na sljedeću lokaciju u stogu u RAM-u. Kada se sadržaj registra (ili vrijednost u jednom operandu) izbaci iz stoga u registar, broj u pokazivaču RSP stoga se povećava za 8. Operativni sustav odlučuje o veličini stoga i gdje počinje u RAM-u i raste prema dolje. Upamtite da je stog struktura Last-In-First-Out (LIFO) koja u ovom slučaju raste prema dolje i skuplja se prema gore.

Da gurnete sadržaj µP RBX registra u stog, učinite sljedeće:

PUSH RBX

Da biste posljednji unos u stogu vratili u RBX, učinite sljedeće:

POP RBX

6.38 Procedura u x64

Potprogram u x64 naziva se 'procedura'. Stog se ovdje koristi više nego što se koristi za 6502 µP. Sintaksa za x64 proceduru je:

proc_name:

tijelo postupka

…

pravo

Prije nego što nastavite, primijetite da operativni kodovi i oznake za x64 potprogram (općenito govoreći o jezičnim uputama za asembler) ne razlikuju velika i mala slova. To jest proc_name je isti kao PROC_NAME. Kao kod 6502, ime procedure (oznaka) počinje na početku novog retka u uređivaču teksta za asemblerski jezik. Nakon toga slijedi dvotočka, a ne razmak i operativni kod kao kod 6502. Slijedi tijelo potprograma koje završava s RET, a ne RTS kao kod 6502 µP. Kao i kod 6502, svaka instrukcija u tijelu, uključujući RET, ne počinje na početku svoje linije. Imajte na umu da oznaka ovdje može imati više od 8 znakova. Za pozivanje ove procedure, iznad ili ispod upisane procedure, učinite sljedeće:

CALL proc_name

Kod 6502, naziv oznake je samo tip za pozivanje. Međutim, ovdje se upisuje rezervirana riječ 'CALL' ili 'poziv', iza koje slijedi naziv procedure (potprograma) nakon razmaka.

Kada se radi o postupcima, obično postoje dva postupka. Jedna procedura poziva drugu. Procedura koja poziva (ima instrukciju poziva) naziva se 'pozivatelj', a procedura koja se poziva naziva se 'pozivatelj'. Postoji konvencija (pravila) koje treba slijediti.

Pravila pozivatelja

Pozivatelj bi se trebao pridržavati sljedećih pravila kada poziva potprogram:

1. Prije poziva potprograma, pozivatelj bi trebao spremiti sadržaj određenih registara koji su označeni kao pozivatelj-spremljeni na stog. Registri koje je spremio pozivatelj su R10, R11 i svi registri u koje su parametri stavljeni (RDI, RSI, RDX, RCX, R8, R9). Ako se sadržaj ovih registara želi sačuvati tijekom poziva potprograma, gurnite ih na stog umjesto da ih spremate u RAM. To se mora učiniti jer pozivatelj mora koristiti registre za brisanje prethodnog sadržaja.

2. Ako je postupak na primjer zbrajanje dvaju brojeva, dva su broja parametri koji se prosljeđuju na stog. Da biste proslijedili parametre potprogramu, stavite ih šest u sljedeće registre redom: RDI, RSI, RDX, RCX, R8, R9. Ako postoji više od šest parametara u potprogramu, gurnite ostatak na stog obrnutim redoslijedom (tj. zadnji parametar prvi). Budući da se stog smanjuje, prvi od dodatnih parametara (zapravo sedmi parametar) pohranjuje se na najnižoj adresi (ova se inverzija parametara povijesno koristila kako bi se omogućilo prosljeđivanje funkcija (potprograma) s promjenjivim brojem parametara).

3. Za pozivanje potprograma (procedure) upotrijebite instrukciju poziva. Ova instrukcija postavlja povratnu adresu na vrh parametara na stogu (najniža pozicija) i grananja koda potprograma.

4. Nakon što se potprogram vrati (tj. odmah nakon instrukcije poziva), pozivatelj mora ukloniti sve dodatne parametre (osim šest koji su pohranjeni u registrima) sa stoga. Ovo vraća stog u stanje prije nego što je poziv izvršen.

5. Pozivatelj može očekivati povratnu vrijednost (adresu) potprograma u RAX registru.

6. Pozivatelj vraća sadržaj registara koje je snimio pozivatelj (R10, R11 i bilo koji u registrima za prosljeđivanje parametara) tako da ih izbaci iz hrpe. Pozivatelj može pretpostaviti da nijedan drugi registar nije modificiran potprogramom.

Zbog načina na koji je konvencija o pozivanju strukturirana, obično je slučaj da neki (ili većina) od ovih koraka neće napraviti nikakve promjene na stogu. Na primjer, ako postoji šest ili manje parametara, ništa se ne gura na stog u tom koraku. Isto tako, programeri (i prevoditelji) obično drže rezultate do kojih im je stalo izvan registara spremljenih pozivatelja u koracima 1 i 6 kako bi spriječili suvišna guranja i iskakanja.

Postoje još dva načina prosljeđivanja parametara potprogramu, ali oni neće biti obrađeni u ovom mrežnom tečaju za karijeru. Jedan od njih koristi sam stog umjesto registara opće namjene.

Pravila pozivatelja

Definicija pozvane podrutine treba se pridržavati sljedećih pravila:

1. Dodijelite lokalne varijable (varijable koje su razvijene unutar procedure) korištenjem registara ili stvaranjem prostora na stogu. Prisjetite se da hrpa raste prema dolje. Dakle, da bi se napravio prostor na vrhu stoga, pokazivač stoga bi trebao biti dekrementiran. Količina za koju se dekrementira pokazivač na stogu ovisi o potrebnom broju lokalnih varijabli. Na primjer, ako su potrebni lokalni float i lokalni long (ukupno 12 bajtova), pokazivač na stogu treba smanjiti za 12 kako bi se napravio prostor za te lokalne varijable. U jeziku visoke razine kao što je C, to znači deklarirati varijable bez dodjele (inicijalizacije) vrijednosti.

2. Zatim, vrijednosti svih registara koji su označeni kao spremljeni za pozivatelja (registri opće namjene koje nije spremio pozivatelj) koje koristi funkcija moraju biti spremljeni. Da biste spremili registre, gurnite ih na stog. Registri spremljeni za pozivatelja su RBX, RBP i R12 do R15 (RSP je također sačuvan konvencijom poziva, ali ne mora biti gurnut na stog tijekom ovog koraka).

Nakon što se izvrše ove tri radnje, može se nastaviti sa stvarnim radom potprograma. Kada je potprogram spreman za povratak, pravila konvencije poziva se nastavljaju.

3. Kada je potprogram gotov, povratnu vrijednost za potprogram treba smjestiti u RAX ako već nije tamo.

4. Potprogram mora vratiti stare vrijednosti svih registara spremljenih od pozivatelja (RBX, RBP i R12 do R15) koji su modificirani. Sadržaj registra se vraća izbacivanjem iz hrpe. Imajte na umu da se registri trebaju otvoriti obrnutim redoslijedom kojim su gurnuti.

5. Zatim oslobađamo lokalne varijable. Najlakši način da to učinite je da RSP-u dodate isti iznos koji je od njega oduzet u 1. koraku.

6. Na kraju se vraćamo pozivatelju izvršavanjem instrukcije ret. Ova uputa će pronaći i ukloniti odgovarajuću povratnu adresu sa stoga.

Primjer tijela podprograma pozivatelja za pozivanje drugog podprograma koji je 'myFunc' je sljedeći (pročitajte komentare):

; Želite nazvati funkciju 'myFunc' koja zahtijeva tri

; cjelobrojni parametar. Prvi parametar je u RAX-u.

; Drugi parametar je konstanta 456. Treći

; parametar je na memorijskoj lokaciji ”variabl”

gurnuti rdi ; rdi će biti param, pa ga spremite

; long retVal = myFunc (x, 456, z);

mov rdi, rax; stavi prvi parametar u RDI

mov rsi, 456; stavi drugi parametar u RSI

mov rdx, [varijabl]; stavi treći parametar u RDX

nazovi myFunc ; pozvati funkciju

pop rdi ; vratiti spremljenu RDI vrijednost

; povratna vrijednost myFunc sada je dostupna u RAX-u

Primjer callee funkcije (myFunc) je (pročitajte komentare):

myFunc :

; ∗∗∗ Standardni prolog potprograma ∗∗∗

sub rsp, 8; prostor za 64-bitnu lokalnu varijablu (rezultat) koristeći 'pod' operativni kod

push rbx ; spremiti callee-spremiti registre

pritisnuti rbp; oba će koristiti myFunc

; ∗∗∗ Podrutina Tijelo ∗∗∗

mov rax, rdi; parametar 1 na RAX

mov rbp, rsi; parametar 2 na RBP

mov rbx, rdx; parametar 3 do rb x

mov [rsp+16], rbx; stavi rbx u lokalnu varijablu

dodati [rsp + 1 6], rbp; dodajte rbp u lokalnu varijablu

mov rax, [rsp +16]; mov sadržaj lokalne varijable u RAX

; (povratna vrijednost/konačni rezultat)

; ∗∗∗ Standardni epilog potprograma ∗∗∗

pop rbp; oporaviti callee spremiti registre

pop rbx; obrnuto od gurnutog

dodati rsp, 8; osloboditi lokalne varijable(e). 8 znači 8 bajtova

ret ; iskoči gornju vrijednost iz gomile, skoči tamo

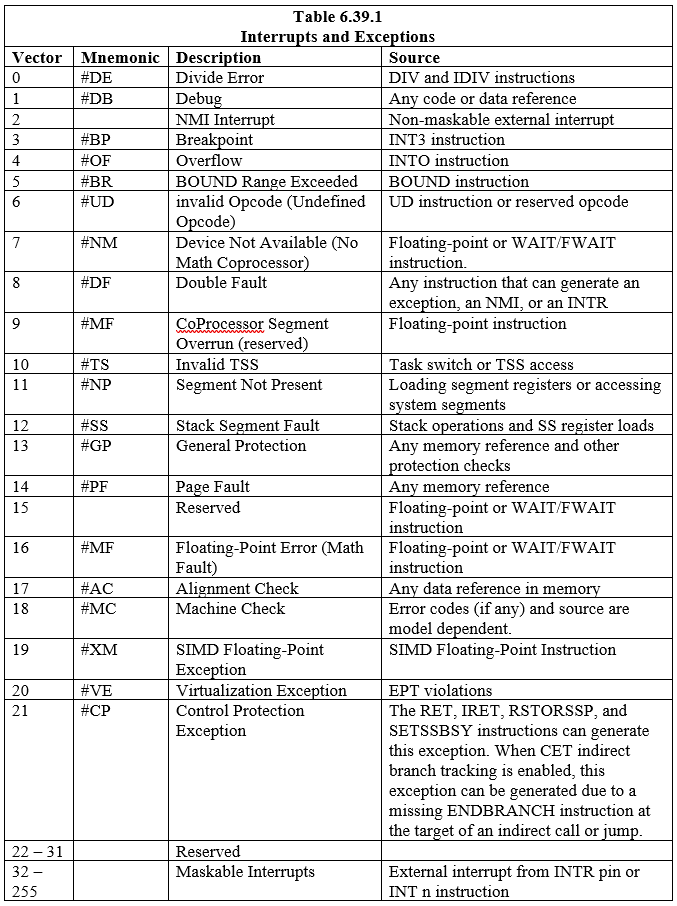

6.39 Prekidi i iznimke za x64

Procesor ima dva mehanizma za prekid izvođenja programa, prekide i iznimke:

- Prekid je asinkroni (može se dogoditi u bilo kojem trenutku) događaj koji obično pokreće I/O uređaj.

- Izuzetak je sinkroni događaj (događa se dok se kod izvršava, unaprijed programiran, na temelju neke pojave) koji se generira kada procesor otkrije jedan ili više unaprijed definiranih uvjeta tijekom izvršavanja instrukcije. Specificirane su tri klase iznimaka: greške, zamke i prekidi.

Procesor odgovara na prekide i iznimke u biti na isti način. Kada se signalizira prekid ili iznimka, procesor zaustavlja izvršenje trenutnog programa ili zadatka i prebacuje se na proceduru rukovatelja koja je posebno napisana za obradu stanja prekida ili iznimke. Procesor pristupa proceduri rukovatelja kroz unos u tablici deskriptora prekida (IDT). Kada rukovatelj završi s rukovanjem prekidom ili iznimkom, kontrola programa se vraća na prekinuti program ili zadatak.

Operativni sustav, izvršni i/ili upravljački programi uređaja obično rukuju prekidima i iznimkama neovisno o aplikacijskim programima ili zadacima. Aplikacijski programi mogu, međutim, pristupiti rukovateljima prekidima i iznimkama koji su ugrađeni u operativni sustav ili ga izvršiti putem poziva asemblerskog jezika.

Definirano je osamnaest (18) unaprijed definiranih prekida i izuzetaka koji su povezani s unosima u IDT. Dvjesto dvadeset četiri (224) korisnički definirana prekida također se mogu napraviti i povezati sa tablicom. Svaki prekid i izuzetak u IDT-u identificiran je brojem koji se naziva 'vektor'. Tablica 6.39.1 navodi prekide i iznimke s unosima u IDT i njihove odgovarajuće vektore. Vektori od 0 do 8, od 10 do 14 i od 16 do 19 su unaprijed definirani prekidi i iznimke. Vektori 32 do 255 su za softverski definirane prekide (korisničke) koji su ili za softverske prekide ili maskibilne hardverske prekide.

Kada procesor otkrije prekid ili iznimku, čini jednu od sljedećih stvari:

- Izvršite implicitni poziv procedure rukovatelja

- Izvršite implicitni poziv zadatku rukovatelja

6.4 Osnove arhitekture 64-bitnog ARM računala

ARM arhitekture definiraju obitelj RISC procesora koji su prikladni za korištenje u širokom spektru aplikacija. ARM je arhitektura učitavanja/pohranjivanja koja zahtijeva da se podaci učitaju iz memorije u registar prije nego što se s njima može izvršiti bilo kakva obrada kao što je ALU (Aritmetičko-logička jedinica) operacija. Sljedeća instrukcija pohranjuje rezultat natrag u memoriju. Iako se ovo može činiti kao korak unatrag u odnosu na arhitekture x86 i x64, koje djeluju izravno na operande u memoriji u jednoj instrukciji (koristeći registre procesora, naravno), pristup učitavanje/pohranjivanje u praksi dopušta nekoliko uzastopnih operacija koja se izvodi velikom brzinom na operandu nakon što se učita u jedan od mnogih registara procesora. ARM procesori imaju opciju little endianness ili big-endianness. Zadana postavka ARM 64 je little-endian, što je konfiguracija koju obično koriste operativni sustavi. 64-bitna ARM arhitektura je moderna i postavljena je da zamijeni 32-bitnu ARM arhitekturu.

Bilješka : Svaka instrukcija za 64-bitni ARM µP duga je 4 bajta (32 bita).

6.41 64-bitni ARM registarski skup

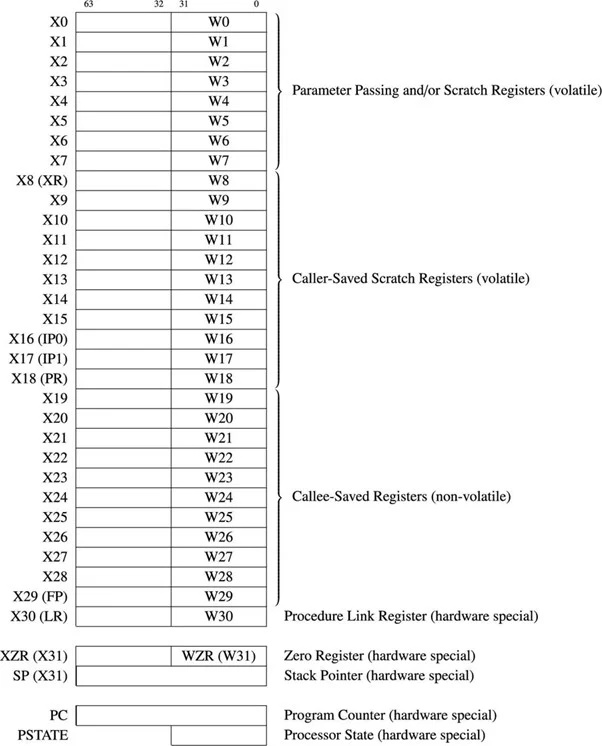

Postoji 31 64-bitni registar opće namjene za 64-bitni ARM µP. Sljedeći dijagram prikazuje registre opće namjene i neke važne registre:

Slika 4.11.1 64-bitni opće namjene i neki važni registri

Registri opće namjene nazivaju se od X0 do X30. Prvi 32-bitni dio za svaki registar se naziva W0 do W30. Kada se ne naglašava razlika između 32 bita i 64 bita, koristi se prefiks “R”. Na primjer, R14 se odnosi na W14 ili X14.

6502 µP ima 16-bitni programski brojač i može adresirati 2 16 memorijske lokacije bajtova. 64-bitni ARM µP ima 64-bitni programski brojač i može adresirati do 2 64 = 1,844674407 x 1019 (zapravo 18,446,744,073,709,551,616) memorijskih bajt lokacija. Programski brojač sadrži adresu sljedeće instrukcije koju treba izvršiti. Dužina instrukcije ARM64 ili AArch64 je obično četiri bajta. Procesor automatski povećava ovaj registar za četiri nakon svake instrukcije dohvaćene iz memorije.

Stack Pointer registar ili SP nije među 31 registrom opće namjene. Pokazivač steka bilo koje arhitekture pokazuje na zadnji unos steka u memoriji. Za ARM-64, hrpa raste prema dolje.

6502 µP ima 8-bitni registar statusa procesora. Ekvivalent u ARM64 se zove PSTATE registar. Ovaj registar pohranjuje oznake koje se koriste za rezultate operacija i za upravljanje procesorom (µP). Širok je 32 bita. Sljedeća tablica daje imena, indekse i značenja često korištenih bitova u registru PSTATE:

| Tablica 6.41.1 Najčešće korištene zastavice PSTATE (bitovi) |

||

|---|---|---|

| Simbol | bit | Svrha |

| M | 0-3 | Način rada: Trenutna razina privilegije izvršenja (USR, SVC itd.). |

| T | 4 | Thumb: Postavlja se ako je skup instrukcija T32 (Thumb) aktivan. Ako je jasno, skup instrukcija ARM je aktivan. Korisnički kod može postaviti i izbrisati ovaj bit. |

| I | 9 | Endianness: Postavljanjem ovog bita omogućuje se način big-endian. Ako je jasno, aktivan je način rada little-endian. Zadani je način rada little-endian. |

| Q | 27 | Oznaka kumulativne zasićenosti: Postavlja se ako u nekom trenutku u nizu operacija dođe do preljeva ili zasićenja |

| U | 28 | Oznaka preljeva: postavlja se ako je operacija rezultirala potpisanim preljevom. |

| C | 29 | Oznaka prijenosa: označava je li zbrajanje proizvelo prijenos ili oduzimanje posuđivanje. |

| S | 30 | Oznaka nula: postavlja se ako je rezultat operacije nula. |

| N | 31 | Negativna zastavica: postavlja se ako je rezultat operacije negativan. |

ARM-64 µP ima mnogo drugih registara.

SIMD

SIMD je kratica za Single Instruction, Multiple Data. To znači da jedna instrukcija asemblerskog jezika može djelovati na više podataka u isto vrijeme u jednom mikroprocesoru. Postoje trideset i dva registra širine 128 bita za korištenje sa SIMD i operacijama s pomičnim zarezom.

6.42 Mapiranje memorije

I RAM i DRAM su memorije s izravnim pristupom. DRAM radi sporije od RAM-a. DRAM je jeftiniji od RAM-a. Ako u memoriji ima više od 32 gigabajta (GB) neprekidnog DRAM-a, bit će više problema s upravljanjem memorijom: 32 GB = 32 x 1024 x 1024 x 1024 bajta. Za cijeli memorijski prostor koji je daleko veći od 32 GB, DRAM iznad 32 GB trebao bi biti isprepleten s RAM-ovima radi boljeg upravljanja memorijom. Kako biste razumjeli memorijsku mapu ARM-64, prvo biste trebali razumjeti mapu memorije od 4 GB za 32-bitnu ARM središnju procesorsku jedinicu (CPU). CPU znači µP. Za 32-bitno računalo maksimalni memorijski adresabilni prostor je 2 32 = 4 x 2 10 x 2 10 x 2 10 = 4 x 1024 x 1024 x 1024 = 4,294,967,296 = 4 GB.

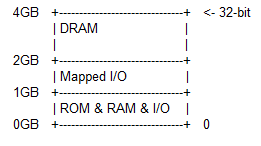

32-bitna mapa ARM memorije

Mapa memorije za 32-bitni ARM je:

Za 32-bitno računalo maksimalna veličina cijele memorije je 4 GB. Od adrese od 0 GB do adrese od 1 GB nalaze se ROM operativni sustav, RAM i I/O lokacije. Cijela ideja ROM OS-a, RAM-a i I/O adresa slična je situaciji s Commodore-64 s mogućim 6502 CPU-om. OS ROM za Commodore-64 nalazi se na vrhu memorijskog prostora. ROM OS ovdje je puno veći od onog kod Commodore-64, i nalazi se na početku cijelog memorijskog adresnog prostora. U usporedbi s drugim modernim računalima, ROM OS ovdje je kompletan, u smislu da je usporediv s količinom OS-a na njihovim tvrdim diskovima. Postoje dva glavna razloga za korištenje OS-a u integriranim krugovima ROM-a: 1) ARM CPU-ovi se uglavnom koriste u malim uređajima poput pametnih telefona. Mnogi tvrdi diskovi veći su od pametnih telefona i drugih malih uređaja, 2) radi sigurnosti. Kada je OS u memoriji samo za čitanje, hakeri ga ne mogu oštetiti (prebrisati dijelove). RAM sekcije i ulazno/izlazne sekcije također su vrlo velike u usporedbi s onima kod Commodore-64.

Kada se uključi napajanje s 32-bitnim ROM OS-om, OS se mora pokrenuti (pokrenuti s) adrese 0x00000000 ili adrese 0xFFFF0000 ako je omogućen HiVECs. Dakle, kada se napajanje uključi nakon faze resetiranja, CPU hardver učitava 0x00000000 ili 0xFFFF0000 u programski brojač. Prefiks “0x” znači heksadecimalno. Adresa pokretanja ARMv8 64-bitnih procesora je definirana implementacija. Međutim, autor savjetuje računalnog inženjera da počne od 0x00000000 ili 0xFFFF0000 radi kompatibilnosti unazad.

Od 1GB do 2GB je mapirani ulaz/izlaz. Postoji razlika između mapiranog I/O i samo I/O koji se nalaze između 0GB i 1GB. Kod I/O, adresa za svaki port je fiksna kao kod Commodore-64. S mapiranim I/O, adresa za svaki port nije nužno ista za svaku operaciju računala (dinamička).

Od 2 GB do 4 GB je DRAM. Ovo je očekivani (ili uobičajeni) RAM. DRAM je kratica za Dynamic RAM, a ne u smislu promjene adrese tijekom rada računala, već u smislu da se vrijednost svake ćelije u fizičkom RAM-u mora osvježiti pri svakom taktu.

Bilješka :

- Od 0x0000,0000 do 0x0000, FFFF je OS ROM.

- Od 0x0001,0000 do 0x3FFF,FFFF, može biti više ROM-a, zatim RAM-a, a zatim nešto I/O.

- Od 0x4000,0000 do 0x7FFF,FFFF, dopušten je dodatni I/O i/ili mapirani I/O.

- Od 0x8000,0000 do 0xFFFF, FFFF je očekivani DRAM.

To znači da očekivani DRAM u praksi ne mora početi na granici od 2 GB memorije. Zašto bi programer trebao poštovati idealne granice kada nema dovoljno fizičkih RAM banaka koje su umetnute na matičnu ploču? To je zato što kupac nema dovoljno novca za sve RAM banke.

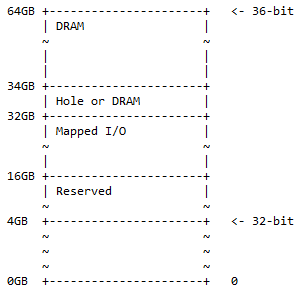

36-bitna ARM memorijska karta

Za 64-bitno ARM računalo, svih 32 bita koriste se za adresiranje cijele memorije. Za 64-bitno ARM računalo, prvih 36 bita može se koristiti za adresiranje cijele memorije koja je u ovom slučaju 2 36 = 68,719,476,736 = 64 GB. Ovo je već puno sjećanja. Današnja obična računala ne trebaju ovu količinu memorije. Ovo još nije dostiglo maksimalni raspon memorije kojoj se može pristupiti putem 64 bita. Mapa memorije za 36-bita za ARM CPU je:

Od adrese od 0 GB do adrese od 4 GB nalazi se 32-bitna memorijska mapa. 'Rezervirano' znači da se ne koristi i čuva se za buduću upotrebu. Ne moraju biti fizičke memorijske banke koje su umetnute na matičnu ploču za taj prostor. Ovdje DRAM i mapirani I/O imaju ista značenja kao i za 32-bitnu memorijsku mapu.

U praksi se može sresti sljedeća situacija:

- 0x1 0000 0000 – 0x3 FFFF FFFF; Rezervirano. 12 GB adresnog prostora rezervirano je za buduću upotrebu.

- 0x4 0000 0000 – 0x7 FFFF FFFF; mapirani I/O. 16 GB adresnog prostora dostupno je za dinamički mapirani I/O.

- 0x8 0000 0000 – 0x8 7FFF FFFF FFFF; Rupa ili DRAM. 2 GB adresnog prostora može sadržavati nešto od sljedećeg:

- Rupa za omogućavanje particioniranja DRAM uređaja (kao što je opisano u sljedećoj raspravi).

- GUTLJAJ.

- 0x8 8000 0000 – 0xF FFFF FFFF; GUTLJAJ. 30 GB adresnog prostora za DRAM.

Ova memorijska mapa je nadskup 32-bitne adresne mape, s dodatnim prostorom koji se dijeli kao 50% DRAM-a (1/2) s izbornom rupom u njemu i 25% mapiranog I/O prostora i rezerviranog prostora (1/4 ). Preostalih 25% (1/4) je za 32-bitnu memorijsku mapu ½ + ¼ + ¼ = 1.

Bilješka : Od 32 bita do 360 bita je dodatak od 4 bita na najznačajniju stranu od 36 bita.

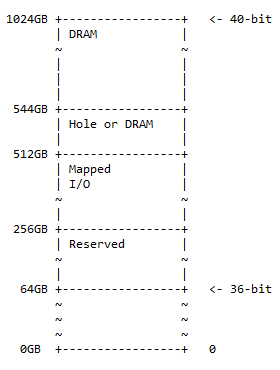

40-bitna memorijska karta

40-bitna adresna mapa nadskup je 36-bitne adresne mape i slijedi isti obrazac od 50% DRAM-a s izbornom rupom u njoj, 25% mapiranog I/O prostora i rezerviranog prostora, te ostatak od 25% prostor za prethodnu memorijsku mapu (36-bitna). Dijagram za memorijsku mapu je:

Veličina rupe je 544 – 512 = 32GB. U praksi se može sresti sljedeća situacija:

- 0x10 0000 0000 – 0x3F FFFF FFFF; Rezervirano. 192 GB adresnog prostora rezervirano je za buduću upotrebu.

- 0x40 0000 0000 – 0x7F FFFF FFFF; mapirano. I/O 256 GB adresnog prostora dostupno je za dinamički mapirani I/O.

- 0x80 0000 0000 – 0x87 FFFF FFFF; rupu ili DRAM. 32 GB adresnog prostora može sadržavati nešto od sljedećeg:

- Rupa za omogućavanje particioniranja DRAM uređaja (kao što je opisano u sljedećoj raspravi)

- GUTLJAJ

- 0x88 0000 0000 – 0xFF FFFF FFFF; GUTLJAJ. 480 GB adresnog prostora za DRAM.

Bilješka : Od 36 bita do 40 bita je dodatak od 4 bita na najznačajniju stranu od 36 bita.

Otvor za DRAM

U memorijskoj mapi iznad 32 bita, to je ili DRAM rupa ili nastavak DRAM-a s vrha. Kada se radi o rupi, treba je cijeniti na sljedeći način: rupa u DRAM-u pruža način da se veliki DRAM uređaj podijeli na više raspona adresa. Opcijska DRAM rupa predložena je na početku više granice DRAM adrese. To omogućuje pojednostavljenu shemu dekodiranja pri particioniranju DRAM uređaja velikog kapaciteta preko niže fizički adresirane regije.

Na primjer, dio DRAM-a od 64 GB dalje je podijeljen u tri regije s pomacima adrese izvedenim jednostavnim oduzimanjem u bitovima adrese višeg reda kako slijedi:

| Tablica 6.42.1 Primjer 64GB DRAM particioniranja s rupama |

|||

|---|---|---|---|

| Fizičke adrese u SoC-u | Pomak | Interna DRAM adresa | |

| 2 GB (32-bitna karta) | 0x00 8000 0000 – 0x00 FFFF FFFF | -0x00 8000 0000 | 0x00 0000 0000 – 0x00 7FFF FFFF |

| 30 GB (36-bitna karta) | 0x08 8000 0000 – 0x0F FFFF FFFF | -0x08 0000 0000 | 0x00 8000 0000 – 0x07 FFFF FFFF |

| 32 GB (40-bitna karta) | 0x88 0000 0000 – 0x8F FFFF FFFF | -0x80 0000 0000 | 0x08 0000 0000 – 0x0F FFFF FFFF |

Predložene 44-bitne i 48-bitne mape adresirane memorije za ARM CPU-e

Pretpostavimo da osobno računalo ima 1024 GB (= 1 TB) memorije; to je previše memorije. I tako, 44-bitne i 48-bitne adresirane memorijske mape za ARM procesore za 16 TB odnosno 256 TB samo su prijedlozi za buduće potrebe računala. Zapravo, ovi prijedlozi za ARM procesore slijede istu podjelu memorije prema omjeru kao i prethodne memorijske karte. To je: 50% DRAM-a s izbornom rupom u njemu, 25% mapiranog I/O prostora i rezerviranog prostora, a ostatak od 25% prostora za prethodnu mapu memorije.

52-bitne, 56-bitne, 60-bitne i 64-bitne mape adresirane memorije tek treba predložiti za ARM 64 bita za daleku budućnost. Ako znanstvenici u to vrijeme još uvijek smatraju da je podjela cjelokupnog memorijskog prostora u omjeru 50 : 25 : 25 korisna, oni će zadržati taj omjer.

Bilješka : SoC je kratica za System-on-Chip što se odnosi na sklopove u µP čipu koji inače ne bi bili tamo.

SRAM ili statička memorija s izravnim pristupom brža je od tradicionalnijeg DRAM-a, ali zahtijeva više silikonske površine. SRAM ne zahtijeva osvježavanje. Čitatelj može zamisliti RAM kao SRAM.

6.43 Načini adresiranja asemblerskog jezika za ARM 64

ARM je arhitektura učitavanja/pohranjivanja koja zahtijeva da se podaci učitaju iz memorije u registar procesora prije nego što se s njima može izvršiti bilo kakva obrada kao što je aritmetičko-logička operacija. Sljedeća instrukcija pohranjuje rezultat natrag u memoriju. Iako se ovo može činiti kao korak unazad u odnosu na x86 i njegove naknadne x64 arhitekture, koje djeluju izravno na operande u memoriji u jednoj instrukciji, u praksi, pristup učitavanja/pohranjivanja dopušta nekoliko uzastopnih operacija koje se izvode velikom brzinom na operand nakon što se učita u jedan od mnogih registara procesora.

Format asemblerskog jezika ARM ima sličnosti i razlika sa serijom x64 (x86).

- Pomak : Konstanta s predznakom može se dodati osnovnom registru. Pomak se upisuje kao dio instrukcije. Na primjer: ldr x0, [rx, #10] učitava r0 s riječi na adresi r1+10.

- Registar : Inkrement bez predznaka koji je pohranjen u registru može se dodati ili oduzeti od vrijednosti u osnovnom registru. Na primjer: ldr r0, [x1, x2] učitava r0 s riječju na adresi x1+x2. Bilo koji od registara može se smatrati osnovnim registrom.

- Skalirani registar : Povećanje u registru pomiče se lijevo ili desno za određeni broj bitovskih pozicija prije dodavanja ili oduzimanja vrijednosti osnovnog registra. Na primjer: ldr x0, [x1, x2, lsl #3] učitava r0 s riječju na adresi r1+(r2×8). Pomak može biti logički pomak ulijevo ili udesno (lsl ili lsr) koji umeće nula bitova na ispražnjene pozicije bitova ili aritmetički pomak udesno (asr) koji replicira bit predznaka na ispražnjene pozicije.

Kada su uključena dva operanda, odredište dolazi prije (lijevo) izvora (postoje neke iznimke). Operacijski kodovi za asemblerski jezik ARM ne razlikuju velika i mala slova.

Trenutno ARM64 način adresiranja

Primjer:

mov r0, #0xFF000000; Učitajte 32-bitnu vrijednost FF000000h u r0

Decimalna vrijednost je bez 0x, ali joj još uvijek prethodi #.

Registrirajte se izravno

Primjer:

mov x0, x1; Kopiraj x1 u x0

Registrirajte se neizravno

Primjer:

str x0, [x3] ; Pohranite x0 na adresu u x3

Registrirajte neizravno s pomakom

Primjeri:

ldr x0, [x1, #32] ; Učitaj r0 s vrijednošću na adresi [r1+32]; r1 je osnovni registar

str x0, [x1, #4] ; Pohranite r0 na adresu [r1+4]; r1 je osnovni registar; brojevi su osnova 10

Registrirajte neizravno s pomakom (unaprijed povećano)

Primjeri:

ldr x0, [x1, #32]! ; Učitaj r0 s [r1+32] i ažuriraj r1 na (r1+32)

str x0, [x1, #4]! ; Pohranite r0 u [r1+4] i ažurirajte r1 u (r1+4)

Obratite pažnju na korištenje '!' simbol.

Registrirajte neizravno s pomakom (naknadno uvećano)

Primjeri:

ldr x0, [x1], #32 ; Učitaj [x1] u x0, zatim ažuriraj x1 u (x1+32)

str x0, [x1], #4 ; Pohranite x0 u [x1], zatim ažurirajte x1 u (x1+4)

Dvostruki registar neizravno

Adresa operanda je zbroj baznog registra i inkrementalnog registra. Nazivi registara su u uglastim zagradama.

Primjeri:

ldr x0, [x1, x2] ; Učitaj x0 s [x1+x2]

str x0, [rx, x2] ; Pohrani x0 do [x1+x2]

Način relativnog adresiranja

U načinu relativnog adresiranja, učinkovita instrukcija je sljedeća instrukcija u programskom brojaču, plus indeks. Indeks može biti pozitivan ili negativan.

Primjer:

ldr x0, [pc, #24]

To znači registar učitavanja X0 s riječju na koju pokazuje PC sadržaj plus 24.

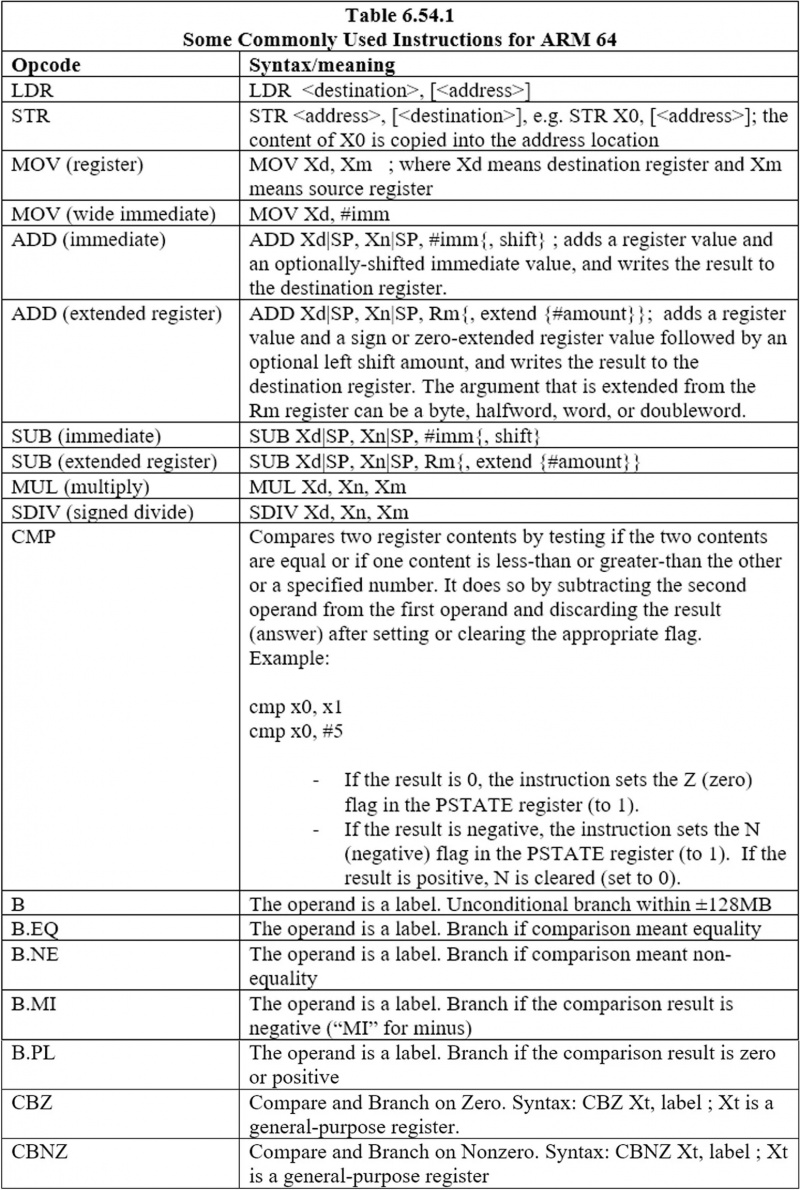

6.44 Neke najčešće korištene upute za ARM 64

Ovo su upute koje se najčešće koriste:

6.45 Looping

Ilustracija

Sljedeći kod dodaje vrijednost u registru X10 vrijednosti u X9 sve dok vrijednost u X8 ne bude nula. Pretpostavimo da su sve vrijednosti cijeli brojevi. Vrijednost u X8 oduzima se za 1 u svakoj iteraciji:

petlja:

CBZ X8, preskoči

DODAJ X9, X9, X10 ; prvi X9 je odredište, a drugi X9 je izvor

SUB X8, X8, #1; prvi X8 je odredište, a drugi X8 je izvor

B petlja

preskočiti:

Kao i kod 6502 µP i X64 µP, oznaka u ARM 64 µP počinje na početku retka. Ostatak uputa počinje na nekoliko mjesta nakon početka retka. Kod x64 i ARM 64 iza oznake slijedi dvotočka i novi red. Dok kod 6502 iza oznake slijedi uputa nakon razmaka. U prethodnom kodu, prva instrukcija koja je 'CBZ X8, preskoči' znači da ako je vrijednost u X8 nula, nastavite na oznaku 'preskoči:', preskačući instrukcije između i nastavljajući s ostatkom uputa ispod 'preskočiti:'. “B petlja” je bezuvjetni skok na oznaku “petlja”. Bilo koji drugi naziv oznake može se koristiti umjesto 'petlje'.

Dakle, kao i kod 6502 µP, upotrijebite upute za grananje da biste imali petlju s ARM 64.

6.46 ARM 64 ulaz/izlaz

Sve ARM periferije (unutarnji priključci) su mapirane u memoriju. To znači da je programsko sučelje skup memorijski adresiranih registara (unutarnji portovi). Adresa takvog registra je pomak od specifične adrese baze memorije. Ovo je slično načinu na koji 6502 radi ulaz/izlaz. ARM nema opciju za odvojeni I/O adresni prostor.

6.47 Hrpa ARM 64

ARM 64 ima hrpu u memoriji (RAM) na sličan način na koji imaju 6502 i x64. Međutim, s ARM64 ne postoji push ili pop opcode. Stog u ARM 64 također raste prema dolje. Adresa u pokazivaču stoga pokazuje neposredno nakon posljednjeg bajta posljednje vrijednosti koja je smještena u stog.

Razlog zašto ne postoji generički pop ili push opcode za ARM64 je taj što ARM 64 upravlja svojim stogom u grupama od uzastopnih 16 bajtova. Međutim, vrijednosti postoje u grupama bajtova od jednog bajta, dva bajta, četiri bajta i 8 bajta. Dakle, jedna vrijednost se može smjestiti u stog, a ostala mjesta (lokacije bajtova) da bi se nadoknadilo 16 bajtova dopunjena su lažnim bajtovima. Ovo ima nedostatak trošenja memorije. Bolje rješenje je ispuniti 16-bajtnu lokaciju s manjim vrijednostima i dati nekom programeru da napiše kod koji prati odakle dolaze vrijednosti u 16-bajtnoj lokaciji (registri). Ovaj dodatni kod također je potreban za povlačenje vrijednosti. Alternativa ovome je ispuniti dva 8-bajtna registra opće namjene s različitim vrijednostima, a zatim poslati sadržaj dva 8-bajtna registra u stog. Ovdje je još uvijek potreban dodatni kod za praćenje specifičnih malih vrijednosti koje ulaze u stog i izlaze iz stoga.

Sljedeći kod pohranjuje četiri 4-bajtna podatka u stog:

str w0, [sp, #-4]!

str w1, [sp, #-8]!

str w2, [sp, #-12]!

str w3, [sp, #-16]!

Prva četiri bajta (w) registara – x0, x1, x2 i x3 – šalju se na lokacije od 16 uzastopnih bajtova u stogu. Obratite pažnju na upotrebu 'str', a ne 'push'. Obratite pažnju na simbol uzvika na kraju svake upute. Budući da memorijski stog raste prema dolje, prva vrijednost od četiri bajta počinje na poziciji koja je minus četiri bajta ispod pozicije pokazivača prethodnog stoga. Ostatak vrijednosti od četiri bajta slijedi, idući prema dolje. Sljedeći segment koda izvršit će ispravan (i redom) ekvivalent iskakanja četiri bajta:

ldr w3, [sp], #0

ldr w2, [sp], #4

ldr w1, [sp], #8

ldr w0, [sp], #12

Obratite pažnju na korištenje ldr opcode umjesto pop. Također imajte na umu da se ovdje ne koristi simbol uzvika.

Svi bajtovi u X0 (8 bajtova) i X1 (8 bajtova) mogu se poslati na lokaciju od 16 bajtova u stogu na sljedeći način:

stp x0, x1, [sp, #-16]! ; 8 + 8 = 16

U ovom slučaju, registri x2 (w2) i x3 (w3) nisu potrebni. Svi traženi bajtovi nalaze se u registrima X0 i X2. Zabilježite stp opcode za spremanje parova sadržaja registara u RAM. Također obratite pozornost na simbol uzvika. Pop ekvivalent je:

ldp x0, x1, [sp], #0

Za ovu uputu nema znaka uzvika. Zabilježite operativni kod LDP umjesto LDR za učitavanje dvije uzastopne podatkovne lokacije iz memorije u dva µP registra. Također zapamtite da je kopiranje iz memorije u µP registar učitavanje, ne treba ga brkati s učitavanjem datoteke s diska u RAM, a kopiranje iz µP registra u RAM je pohranjivanje.

6.48 Potprogram

Potprogram je blok koda koji izvršava zadatak, po izboru na temelju nekih argumenata i po izboru vraća rezultat. Prema konvenciji, registri R0 do R3 (četiri registra) koriste se za prosljeđivanje argumenata (parametara) potprogramu, a R0 se koristi za prosljeđivanje rezultata natrag pozivatelju. Potprogram koji treba više od 4 ulaza koristi stog za dodatne ulaze. Za pozivanje potprograma koristite vezu ili instrukciju uvjetnog grananja. Sintaksa za instrukciju veze je:

BL oznaka

Gdje je BL operativni kod, a labela predstavlja početak (adresu) potprograma. Ova grana je bezuvjetna, naprijed ili nazad unutar 128 MB. Sintaksa za instrukciju uvjetnog grananja je:

B.kond oznaka

Gdje je cond uvjet, npr. eq (jednako) ili ne (nije jednako). Sljedeći program ima potprogram doadd koji zbraja vrijednosti dvaju argumenata i vraća rezultat u R0:

AREA potput, KOD, SAMO ZA ČITANJE ; Imenujte ovaj blok koda

ULAZAK ; Označite prvu instrukciju za izvršenje

početak MOV r0, #10 ; Postavite parametre

MOV r1, #3

BL dodati; Poziv potprograma

zaustavi MOV r0, #0x18 ; angel_SWIreason_ReportException

LDR rl, =0x20026; ADP_Stopped_ApplicationExit

SVC #0x123456 ; ARM semihosting (bivši SWI)

doadd ADD r0, r0, r1 ; Kod potprograma

BX lr ; Povratak iz potprograma

;

KRAJ ; Označi kraj datoteke

Brojevi koje treba dodati su decimalno 10 i decimalno 3. Prva dva retka u ovom bloku koda (programu) bit će objašnjena kasnije. Sljedeća tri retka šalju 10 u registar R0 i 3 u registar R1, te također pozivaju potprogram doadd. 'Doadd' je oznaka koja sadrži adresu početka potprograma.

Potprogram se sastoji od samo dva retka. Prvi redak dodaje sadržaj 3 od R sadržaju 10 od R0 što dopušta rezultat 13 u R0. Drugi redak s BX operativnim kodom i LR operandom vraća se iz potprograma u kod pozivatelja.

PRAVO

RET operativni kod u ARM 64 i dalje se bavi potprogramom, ali radi drugačije od RTS-a u 6502 ili RET-a na x64, ili kombinacije 'BX LR' u ARM-u 64. U ARM-u 64, sintaksa za RET je:

RAVNO {Xn}

Ova instrukcija daje mogućnost programu da nastavi s podprogramom koji nije pozivatelj podprograma ili jednostavno nastavi s nekom drugom instrukcijom i njezinim sljedećim segmentom koda. Xn je registar opće namjene koji sadrži adresu na koju se program treba nastaviti. Ova se uputa grana bezuvjetno. Zadani je sadržaj X30 ako Xn nije dan.

Procedura Call Standard

Ako programer želi da njegov kod bude u interakciji s kodom koji je napisao netko drugi ili s kodom koji je proizveo prevodilac, programer se treba dogovoriti s osobom ili piscem prevoditelja o pravilima za korištenje registra. Za ARM arhitekturu, ova se pravila nazivaju Procedure Call Standard ili PCS. To su dogovori između dvije ili tri strane. PCS navodi sljedeće:

- Koji se µP registri koriste za prosljeđivanje argumenata u funkciju (potprogram)

- Koji se µP registri koriste za vraćanje rezultata funkciji koja poziva a koja je poznata kao pozivatelj

- Koji µP registrira funkciju koja se poziva, a koja je poznata kao callee, može pokvariti

- Koji µP registrira pozvani ne može pokvariti

6.49 Prekidi

Postoje dvije vrste krugova kontrole prekida dostupnih za ARM procesor:

- Standardni kontroler prekida: Rukovatelj prekida određuje koji uređaj zahtijeva servisiranje čitanjem registra bitmape uređaja u kontroleru prekida.

- Vector Interrupt Controller (VIC): daje prioritet prekidima i pojednostavljuje određivanje uređaja koji je uzrokovao prekid. Nakon povezivanja prioriteta i adrese rukovatelja sa svakim prekidom, VIC samo potvrđuje signal prekida procesoru ako je prioritet novog prekida veći od trenutnog izvršavanja rukovatelja prekidima.

Bilješka : Iznimka se odnosi na pogrešku. Detalji za vektorski kontroler prekida za 32-bitno ARM računalo su sljedeći (64-bitni je sličan):

| Tablica 6.49.1 ARM vektorska iznimka/prekid za 32-bitno računalo |

|||

|---|---|---|---|

| Iznimka/prekid | Kratka ruka | Adresa | Visoka adresa |

| Resetiraj | RESETIRANJE | 0x00000000 | 0xffff0000 |

| Nedefinirana instrukcija | UNDEF | 0x00000004 | 0xffff0004 |

| Softverski prekid | SWI | 0x00000008 | 0xffff0008 |

| Unaprijed dohvati prekid | pabt | 0x0000000C | 0xffff000C |

| Datum pobačaja | DABT | 0x00000010 | 0xffff0010 |

| Rezervirano | – | 0x00000014 | 0xffff0014 |

| Zahtjev za prekid | IRQ | 0x00000018 | 0xffff0018 |

| Zahtjev za brzi prekid | FIQ | 0x0000001C | 0xffff001C |

Ovo izgleda kao aranžman za arhitekturu 6502 gdje NMI , BR , i IRQ može imati pokazivače na nultoj stranici, a odgovarajuće rutine su visoko u memoriji (ROM OS). Kratki opisi redaka prethodne tablice su sljedeći:

RESETIRANJE

To se događa kada se procesor uključi. Inicijalizira sustav i postavlja nizove za različite načine rada procesora. To je iznimka najvišeg prioriteta. Nakon ulaska u rukovatelj resetiranja, CPSR je u SVC načinu rada i oba bita IRQ i FIQ postavljeni su na 1, maskirajući sve prekide.

DATUM POBAČAJA

Drugi najveći prioritet. To se događa kada pokušamo čitati/pisati na nevažeću adresu ili pristupiti pogrešnoj dozvoli pristupa. Nakon ulaska u Data Abort Handler, IRQ-ovi će biti onemogućeni (I-bit set 1) i FIQ će biti omogućen. IRQ-ovi su maskirani, ali FIQ-ovi ostaju nemaskirani.

FIQ

Prekid najvišeg prioriteta, IRQ & FIQ, onemogućeni su dok se ne obradi FIQ.

IRQ

Prekid visokog prioriteta, IRQ rukovatelj, unosi se samo ako nema tekućeg FIQ-a i prekida podataka.

Pre-Fetch Prekid

Ovo je slično prekidu podataka, ali se događa pri neuspješnom dohvaćanju adrese. Nakon ulaska u rukovatelja, IRQ-ovi su onemogućeni, ali FIQ-ovi ostaju uključeni i mogu se dogoditi tijekom prekida prethodnog dohvaćanja.

SWI

Iznimka softverskog prekida (SWI) događa se kada se izvrši SWI instrukcija, a niti jedna druga iznimka višeg prioriteta nije označena.

Nedefinirana instrukcija

Iznimka Nedefinirana instrukcija događa se kada instrukcija koja nije u ARM ili Thumb skupu instrukcija dosegne fazu izvršenja cjevovoda i nijedna druga iznimka nije označena. Ovo je isti prioritet kao i SWI jer se može dogoditi jedan u jednom trenutku. To znači da instrukcija koja se izvršava ne može istovremeno biti SWI instrukcija i nedefinirana instrukcija.

Rukovanje iznimkama ARM-a

Sljedeći događaji se događaju kada se dogodi iznimka:

- Pohranite CPSR u SPSR načina iznimke.

- PC je pohranjen u LR modu iznimke.

- Registar veze postavljen je na određenu adresu na temelju trenutne instrukcije. Na primjer: za ISR, LR = zadnja izvršena instrukcija + 8.

- Ažurirajte CPSR o iznimci.

- Postavite računalo na adresu rukovatelja iznimkama.

6.5 Upute i podaci

Podaci se odnose na varijable (oznake s njihovim vrijednostima) i nizove i druge strukture koje su slične nizu. Niz je poput niza znakova. Niz cijelih brojeva se vidi u jednom od prethodnih poglavlja. Upute se odnose na operativne kodove i njihove operande. Program se može napisati s operacijskim kodovima i podacima pomiješanim u jednom kontinuiranom dijelu memorije. Taj pristup ima nedostataka, ali se ne preporučuje.

Prvo treba napisati program s uputama, a zatim podacima (množina od podatak je podatak). Razmak između instrukcija i podataka može biti samo nekoliko bajtova. Za program, i upute i podaci mogu biti u jednom ili dva odvojena odjeljka u memoriji.

6.6 Harvardska arhitektura

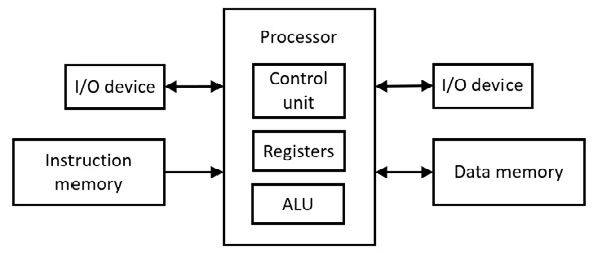

Jedno od prvih računala zove se Harvard Mark I (1944.). Stroga harvardska arhitektura koristi jedan adresni prostor za programske upute i drugi odvojeni adresni prostor za podatke. To znači da postoje dvije odvojene memorije. Sljedeće prikazuje arhitekturu:

Slika 6.71 Harvardska arhitektura

Kontrolna jedinica vrši dekodiranje instrukcija. Aritmetičko-logička jedinica (ALU) izvodi aritmetičke operacije pomoću kombinacijske logike (vrata). ALU također obavlja logičke operacije (npr. mijenjanje stupnjeva prijenosa).

S mikroprocesorom 6502, instrukcija prvo ide mikroprocesoru (kontrolnoj jedinici) prije nego podatak (jednina za podatke) ode u µP registar prije nego što stupe u interakciju. Za to su potrebna najmanje dva taktna impulsa i to nije istovremeni pristup instrukciji i datumu. S druge strane, harvardska arhitektura omogućuje istovremeni pristup uputama i podacima, pri čemu i instrukcija i podatak ulaze u µP u isto vrijeme (operacijski kod za upravljačku jedinicu i podatak za µP registar), čime se štedi najmanje jedan taktni impuls. Ovo je oblik paralelizma. Ovaj oblik paralelizma koristi se u hardverskoj predmemoriji u modernim matičnim pločama (pogledajte sljedeću raspravu).

6.7 Predmemorija

Cache Memory (RAM) je memorijsko područje velike brzine (u usporedbi s brzinom glavne memorije) koje privremeno pohranjuje programske upute ili podatke za buduću upotrebu. Priručna memorija radi brže od glavne memorije. Obično se te upute ili podatkovne stavke dohvaćaju iz nedavne glavne memorije i vjerojatno će vam uskoro ponovno biti potrebne. Primarna svrha predmemorije je povećati brzinu opetovanog pristupa istim mjestima glavne memorije. Da bi bio učinkovit, pristup predmemoriranim stavkama mora biti znatno brži od pristupa izvornom izvoru uputa ili podataka koji se naziva Backing Store.

Kada se koristi predmemorija, svaki pokušaj pristupa glavnoj memorijskoj lokaciji počinje pretraživanjem predmemorije. Ako je tražena stavka prisutna, procesor je dohvaća i odmah koristi. To se zove Cache Hit. Ako je pretraživanje predmemorije neuspješno (promašaj predmemorije), instrukcija ili podatkovna stavka moraju se dohvatiti iz rezervne memorije (glavne memorije). U procesu dohvaćanja tražene stavke, kopija se dodaje u predmemoriju za predviđenu upotrebu u bliskoj budućnosti.

Jedinica za upravljanje memorijom

Jedinica za upravljanje memorijom (MMU) je sklop koji upravlja glavnom memorijom i povezanim memorijskim registrima na matičnoj ploči. U prošlosti je to bio zaseban integrirani sklop na matičnoj ploči; ali danas je tipično dio mikroprocesora. MMU bi također trebao upravljati cache memorijom (sklopom) koja je danas također dio mikroprocesora. Sklop predmemorije je u prošlosti bio zaseban integrirani sklop.

Statički RAM

Statički RAM (SRAM) ima znatno brže vrijeme pristupa od DRAM-a, iako nauštrb znatno složenijih sklopova. SRAM bitne ćelije zauzimaju puno više prostora na matici integriranog kruga nego ćelije DRAM uređaja koji može pohraniti ekvivalentnu količinu podataka. Glavna memorija (RAM) obično se sastoji od DRAM-a (Dynamic RAM).

Predmemorija poboljšava performanse računala jer mnogi algoritmi koje izvršavaju operativni sustavi i aplikacije pokazuju lokalnost reference. Lokalitet reference odnosi se na ponovnu upotrebu podataka kojima se nedavno pristupilo. Ovo se naziva vremenski lokalitet. Na modernoj matičnoj ploči, predmemorija je u istom integriranom krugu kao i mikroprocesor. Glavna memorija (DRAM) je daleko i dostupna je preko sabirnica. Referentni lokalitet također se odnosi na prostorni lokalitet. Prostorni lokalitet ima veze s većom brzinom pristupa podacima zbog fizičke blizine.

U pravilu, regije cache memorije su male (u broju lokacija bajtova) u usporedbi s rezervnom pohranom (glavnom memorijom). Uređaji cache memorije dizajnirani su za maksimalnu brzinu što općenito znači da su složeniji i skuplji po bitu od tehnologije pohranjivanja podataka koja se koristi u pohranjivanju podataka. Zbog svoje ograničene veličine, uređaji predmemorije imaju tendenciju brzog punjenja. Kada predmemorija nema dostupnu lokaciju za spremanje novog unosa, stariji unos se mora odbaciti. Kontroler predmemorije koristi Pravila zamjene predmemorije da odabere koji će unos predmemorije biti prebrisan novim unosom.

Cilj predmemorije mikroprocesora je maksimizirati postotak pogodaka predmemorije tijekom vremena, čime se osigurava najveća održiva stopa izvršavanja instrukcija. Da bi se postigao ovaj cilj, logika predmemoriranja mora odrediti koje će se upute i podaci smjestiti u predmemoriju i zadržati za blisku buduću upotrebu.

Procesorska logika predmemorije ne jamči da će se predmemorirana podatkovna stavka ikada ponovno koristiti nakon što je umetnuta u predmemoriju.

Logika predmemoriranja oslanja se na vjerojatnost da zbog vremenske (ponavljanja tijekom vremena) i prostorne (prostorne) lokacije, postoji vrlo dobra šansa da će se predmemoriranim podacima pristupiti u bliskoj budućnosti. U praktičnim implementacijama na modernim procesorima, pogoci predmemorije obično se javljaju na 95 do 97 posto pristupa memoriji. Budući da je latencija predmemorije mali dio latencije DRAM-a, visoka stopa pogodaka predmemorije dovodi do značajnog poboljšanja performansi u usporedbi s dizajnom bez predmemorije.

Neki paralelizam s predmemorijom

Kao što je ranije spomenuto, dobar program u memoriji ima upute odvojene od podataka. U nekim sustavima predmemorije, postoji krug predmemorije na 'lijevoj' strani procesora i postoji još jedan krug predmemorije na 'desnoj' strani procesora. Lijeva predmemorija obrađuje upute programa (ili aplikacije), a desna predmemorija obrađuje podatke istog programa (ili iste aplikacije). To dovodi do bolje povećane brzine.

6.8 Procesi i niti

I CISC i RISC računala imaju procese. Proces je na softveru. Program koji se izvodi (izvršava) je proces. Operativni sustav dolazi s vlastitim programima. Dok računalo radi, rade i programi operativnog sustava koji omogućuju rad računala. To su procesi operativnog sustava. Korisnik ili programer može pisati vlastite programe. Kada je korisnički program pokrenut, to je proces. Nije važno je li program napisan u asemblerskom jeziku ili u jeziku visoke razine poput C ili C++. Svim procesima (korisničkim ili OS-om) upravlja drugi proces koji se naziva 'planer'.

Nit je poput podprocesa koji pripada procesu. Proces se može pokrenuti i podijeliti u niti, a zatim nastaviti kao jedan proces. Proces bez niti se može smatrati glavnom niti. Procesima i njihovim nitima upravlja isti planer. Sam planer je program kada se nalazi na disku OS-a. Kada se izvodi u memoriji, planer je proces.

6.9 Višestruka obrada

Nitovima se upravlja gotovo kao procesima. Multiprocesiranje znači pokretanje više od jednog procesa u isto vrijeme. Postoje računala sa samo jednim mikroprocesorom. Postoje računala s više od jednog mikroprocesora. S jednim mikroprocesorom, procesi i/ili niti koriste isti mikroprocesor na način ispreplitanja (ili vremenskog odsječka). To znači da proces koristi procesor i zaustavlja se bez završetka. Drugi proces ili nit koristi procesor i zaustavlja se bez završetka. Zatim drugi proces ili nit koristi mikroprocesor i zaustavlja se bez završetka. To se nastavlja sve dok svi procesi i niti koje je raspoređivač stavio u red čekanja ne dobiju udio procesora. To se naziva istodobna višeprocesna obrada.

Kada postoji više od jednog mikroprocesora, postoji paralelna višestruka obrada, za razliku od istovremenosti. U ovom slučaju svaki procesor pokreće određeni proces ili nit, različitu od one koju pokreće drugi procesor. Svi procesori na istoj matičnoj ploči pokreću svoje različite procese i/ili različite niti u isto vrijeme u paralelnom višeprocesiranju. Procesima i nitima u paralelnom višeprocesiranju i dalje upravlja planer. Paralelno višeprocesiranje je brže od istovremenog višeprocesiranja.

U ovom trenutku, čitatelj se može zapitati kako je paralelna obrada brža od istodobne obrade. To je zato što procesori dijele (moraju koristiti u različito vrijeme) istu memoriju i ulazno/izlazne priključke. Pa, uz korištenje predmemorije, ukupni rad matične ploče je brži.

6.10 Paging

Jedinica za upravljanje memorijom (MMU) je krug koji je blizu mikroprocesora ili u mikroprocesorskom čipu. Obrađuje memorijsku kartu ili straničenje i druge probleme s memorijom. Niti 6502 µP niti Commodore-64 računalo nemaju MMU per se (iako još uvijek postoji nešto upravljanja memorijom u Commodore-64). Commodore-64 upravlja memorijom straničenjem gdje svaka stranica ima 256 stranica 10 dužina bajtova (100 16 dužine bajtova). Nije bilo obavezno rukovati memorijom straničenjem. Još uvijek može imati samo memorijsku mapu, a zatim programe koji se samo uklapaju u svoja različita određena područja. Pa, straničenje je jedan od načina pružanja učinkovite upotrebe memorije bez mnogo memorijskih odjeljaka koji ne mogu sadržavati podatke ili programe.

Računalna arhitektura x86 386 objavljena je 1985. Adresna sabirnica široka je 32 bita. Dakle, ukupno 2 32 = moguće je 4,294,967,296 adresnog prostora. Ovaj adresni prostor podijeljen je na 1.048.576 stranica = 1.024 KB stranica. Uz ovaj broj stranica, jedna stranica se sastoji od 4.096 bajtova = 4 KB. Sljedeća tablica prikazuje stranice fizičkih adresa za x86 32-bitnu arhitekturu:

| Tablica 6.10.1 Fizičke adresabilne stranice za x86 arhitekturu |

||

|---|---|---|

| Baza 16 adresa | Stranice | Baza 10 adresa |

| FFFFF000 – FFFFFFFF | Stranica 1.048.575 | 4.294.963.200 – 4.294.967.295 |

| FFFFE000 – FFFFEFFF | Stranica 1.044.479 | 4.294.959.104 – 4.294.963.199 |

| FFFFD000 – FFFFDFFF | Stranica 1.040.383 | 4.294.955.008 – 4.294.959.103 |

| | | | |

| | | |

| | | |

| 00002000 – 00002FFF | stranica 2 | 8.192 – 12.288 |

| 00001000 – 00001FFF | Stranica 1 | 4.096 – 8.191 |

| 00000000 – 00000FFF | Stranica 0 | 0 – 4.095 |

Aplikacija se danas sastoji od više od jednog programa. Jedan program može zauzeti manje od jedne stranice (manje od 4096) ili može zauzeti dvije ili više stranica. Dakle, aplikacija može uzeti jednu ili više stranica gdje je svaka stranica duga 4096 bajtova. Različiti ljudi mogu napisati prijavu, pri čemu je svaka osoba dodijeljena jednoj ili više stranica.

Primijetite da je stranica 0 od 00000000H do 00000FFF

stranica 1 je od 00001000H do 00001FFFH, stranica 2 je od 00002000 H – 00002FFF H , i tako dalje. Za 32-bitno računalo postoje dva 32-bitna registra u procesoru za fizičko adresiranje stranica: jedan za osnovnu adresu, a drugi za indeksnu adresu. Za pristup lokacijama bajtova na stranici 2, na primjer, registar za osnovnu adresu trebao bi biti 00002 H što je prvih 20 bitova (slijeva) za početne adrese stranice 2. Ostali bitovi u rasponu od 000 H na FFF H nalaze se u registru koji se naziva “indeksni registar”. Dakle, svim bajtovima na stranici može se pristupiti samo povećanjem sadržaja u registru indeksa od 000 H na FFF H . Sadržaj u indeksnom registru dodaje se sadržaju koji se ne mijenja u osnovnom registru za dobivanje efektivne adrese. Ova shema adresiranja indeksa vrijedi i za ostale stranice.

Međutim, to nije način na koji je program na asemblerskom jeziku napisan za svaku stranicu. Za svaku stranicu programer piše kod počevši od stranice 000 H na stranicu FFF H . Budući da su kodovi na različitim stranicama povezani, kompajler koristi adresiranje indeksa za povezivanje svih povezanih adresa na različitim stranicama. Na primjer, pod pretpostavkom da su stranica 0, stranica 1 i stranica 2 za jednu aplikaciju i svaka ima 555 H adrese koje su povezane jedna s drugom, kompajler kompajlira na takav način da kada 555 H stranice 0 treba pristupiti, 00000 H bit će u osnovnom registru i 555 H bit će u indeksnom registru. Kada je 555 H stranice 1 treba pristupiti, 00001 H bit će u osnovnom registru i 555 H bit će u indeksnom registru. Kada je 555 H stranici 2 je potrebno pristupiti, 00002 H bit će u osnovnom registru, a 555H u indeksnom registru. To je moguće jer se adrese mogu identificirati pomoću oznaka (varijabli). Različiti programeri moraju se dogovoriti oko imena oznaka koje će se koristiti za različite adrese povezivanja.

Virtualna memorija stranice

Straničenje, kao što je prethodno opisano, može se modificirati kako bi se povećala veličina memorije u tehnici koja se naziva 'Virtualna memorija stranice'. Pod pretpostavkom da sve stranice fizičke memorije, kao što je prethodno opisano, imaju nešto (upute i podatke), nisu sve stranice trenutno aktivne. Stranice koje trenutno nisu aktivne šalju se na tvrdi disk i zamjenjuju stranice s tvrdog diska koje trebaju biti pokrenute. Na taj način se povećava veličina memorije. Kako računalo nastavlja s radom, stranice koje postanu neaktivne zamjenjuju se sa stranicama na tvrdom disku koje još uvijek mogu biti stranice koje su poslane iz memorije na disk. Sve to radi jedinica za upravljanje memorijom (MMU).

6.11 Problemi

Čitatelju se savjetuje da riješi sve probleme u poglavlju prije nego prijeđe na sljedeće poglavlje.

1) Navedite sličnosti i razlike računalnih arhitektura CISC i RISC. Navedite po jedan primjer SISC i RISC računala.

2) a) Koji su sljedeći nazivi za CISC računalo u smislu bitova: bajt, riječ, dvostruka riječ, četveroriječ i dvostruka četveroriječ.

b) Koji su sljedeći nazivi za RISC računalo u smislu bitova: bajt, poluriječ, riječ i dvostruka riječ.

c) Da ili Ne. Znače li dvostruka riječ i četveroriječ isto u CISC i RISC arhitekturi?

3 a) Za x64, broj bajtova za instrukcije asemblerskog jezika kreće se od što do čega?

b) Je li broj bajtova za sve instrukcije asemblerskog jezika za ARM 64 fiksan? Ako da, koji je broj bajtova za sve instrukcije?

4) Navedite najčešće korištene instrukcije asemblerskog jezika za x64 i njihova značenja.

5) Navedite najčešće korištene instrukcije asemblerskog jezika za ARM 64 i njihova značenja.

6) Nacrtajte označeni blok dijagram starog računala Harvard Architecture. Objasnite kako se njegove instrukcije i značajke podataka koriste u predmemoriji modernih računala.

7) Napravite razliku između procesa i niti i navedite naziv procesa koji upravlja procesima i nitima u većini računalnih sustava.

8) Ukratko objasnite što je multiprocesiranje.

9) a) Objasnite straničenje primjenjivo na računalnu arhitekturu x86 386 µP.

b) Kako se ovo straničenje može modificirati da se poveća veličina cijele memorije?